# 浙江大学实验报告

专业: 材料科学与工程

姓名: \_\_\_\_\_

学号: \_\_\_\_\_

日期: 2024.11.12

地点: 东 3-309

课程名称: 电路与电子技术实验 I 指导老师: 王旃 实验类型: 数电实验

实验名称: 数字式时钟 成绩: \_\_\_\_\_ 签名: 无

## 一、实验目的

- 了解数字电路的基本组成，认识数字信号、逻辑电平和逻辑关系；

- 学习数字电子电路的常用调试方法；

- 掌握数制、码制及相互间的转换方法；

- 熟悉集成计数器的逻辑功能、时序分析方法和测试方法。

- 掌握用示波器测量多个波形时序关系的方法。

## 二、实验原理

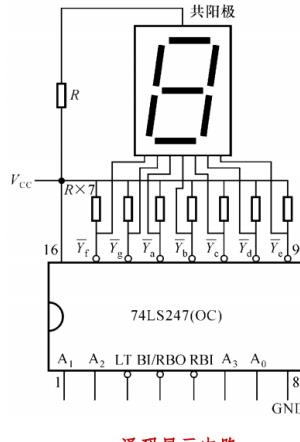

### 1. 数码管

线

订

装

译码显示电路

二极管应串接电阻以防电流过大而烧坏。

实验箱上已将译码器和数码管连接好。

实验箱上的数码管为共阴极，但原理与之相同

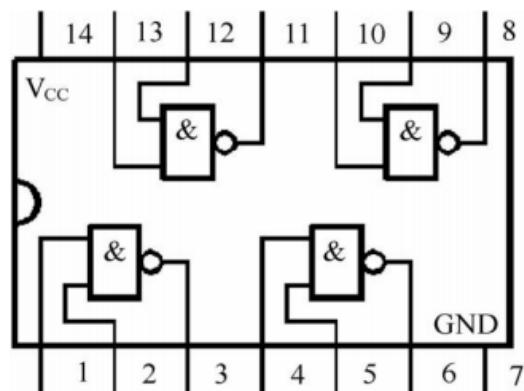

## 2. 74LS00 芯片

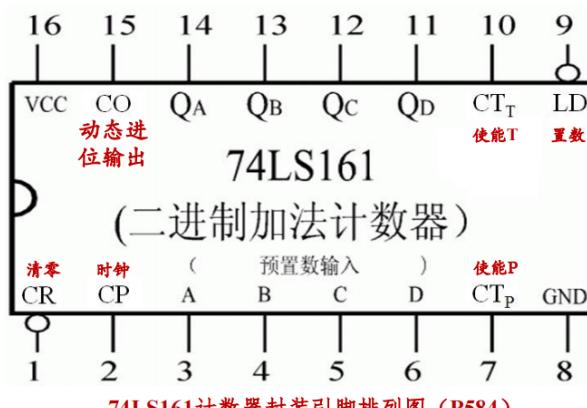

## 3. 74LS161 芯片

74LS161 是常用的四位二进制可预置的同步加法计数器，它可以灵活地运用在各种数字电路以及单片机系统中，实现分频器等很多重要的功能。

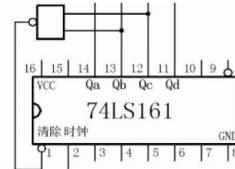

74LS161计数器封装引脚排列图 (P584)

异步清零，

功能最优先

74LS161计数器功能表

| CP      | CR | LD | CT <sub>p</sub> | CT <sub>T</sub> | D | C | B | A | 触发器状态          |                |                |                |

|---------|----|----|-----------------|-----------------|---|---|---|---|----------------|----------------|----------------|----------------|

|         |    |    |                 |                 |   |   |   |   | Q <sub>D</sub> | Q <sub>C</sub> | Q <sub>B</sub> | Q <sub>A</sub> |

| ×       | 0  | ×  | ×               | ×               | × | × | × | × | 0              | 0              | 0              | 0              |

| ↑       | 1  | 0  | ×               | ×               | D | C | B | A | D              | C              | B              | A              |

| ↑       | 1  | 1  | 1               | 1               | × | × | × | × | 4位二进制 加法计数     |                |                |                |

| CP上升沿有效 | 1  | 1  | 0               | ×               | × | × | × | × | 保持功能           |                |                |                |

| ×       | 1  | 1  | ×               | 0               | × | × | × | × | 保持功能           |                |                |                |

$$CO = Q_B \cdot Q_C \cdot Q_D \cdot Q_A \cdot CT_T$$

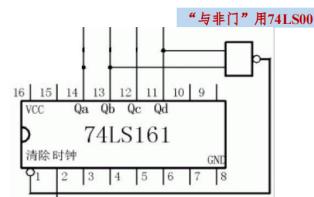

#### 4. 10 进制和 6 进制计数器

10进制、6进制计数器

74LS161接成10进制计数器

74LS161接成6进制计数器

当达到需要进位的数字时，利用与非门输出 0 传递到清零端，使得计数器清零

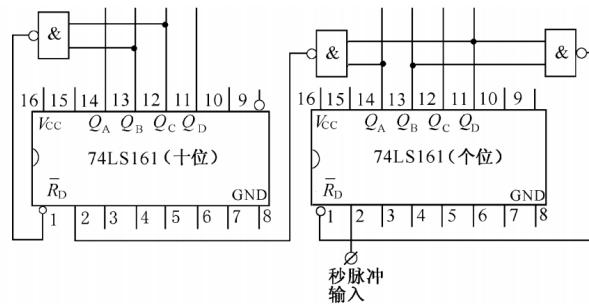

#### 5. 60 进制计数器

秒、分计数器都是 60 进制计数器，由 10 进制计数器和 6 进制计数器级联而成，个位为 10 进制计数器，十位为 6 进制计数器，如图所示。当个位十进制计数器计到 9 后，下一个计数脉冲到达时计数器状态应该回到 0，同时向十位计数器发出上升沿进位信号。因此，个位计数器向十位计数器发出的进位信号  $Z$  是在个位计数器从 (1001) 状态变到 (0000) 状态时发出的，所以进位信号的逻辑表达式为  $Z = Q_D Q_A$ 。60 进制秒计数器与 60 进制分计数器之间的进位信号  $Z$ ，是在 60 进制秒计数器的 (01011001) 状态转换到 (00000000) 状态，即当秒计数器计到 59 秒后，再来一个计数脉冲，使状态回到 00 时发出的，所以 60 进制分计数器的计数输入脉冲  $Z$  的逻辑表达式  $Z = Q_A Q_C$ 。

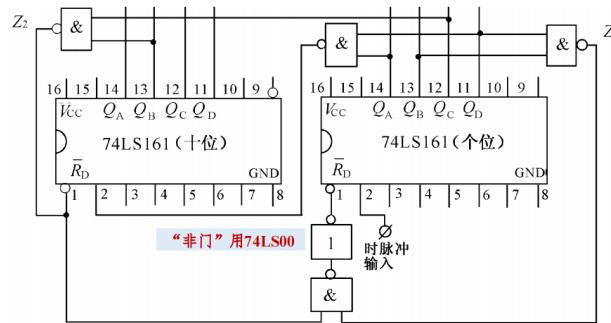

## 6. 24 进制计数器

数字式计时器中的时计数器采用 24 进制计数，个位为 10 进制计数器，十位为 2 进制计数器。当十位的计数值还不到 2(即  $Q_D Q_C Q_B Q_A$  为 0010) 时，个位的计数器应按照十进制的规律进行计数。但当计数到 23 时，若再来一个 CP 脉冲，则应将十位计数器和个位计数器同时清零，从而实现 24 进制计数。所以  $Z_1$  的逻辑表达式为  $Z_1 = Q_{2b} Q_{1c}$ 。

## 三、 主要仪器设备

1. 数字逻辑电路实验箱

2. 74LS00 芯片

3. 74LS161 芯片

## 四、 操作方法与实验步骤

### 1. 测试译码显示电路的功能

在实验箱上译码显示电路部分的 D、C、B、A 端依次输入 0000 1111 代码（使用数据开关），列表记录数码管所显示的数字或形状。

### 2. 测试 74LS00 与非门的功能

将与非门的输出端接发光二极管，输入端接数据开关。接通与非门的电源，观察与非门在不同输入组合下的输出情况并记录。

将实验箱提供的 1Hz 基准频率（或秒信号）送入与非门输入端，输出接发光二极管。控制端 Y 接数据开关，当控制端 Y 分别加上逻辑电平 0 和 1 时，观察 Y 对输出的控制作用。

### 3. 测试 74LS161 计数器的功能

在 CP 端加入手控的逻辑电平信号，输出端（QD、QC、QB、QA）接发光二极管，观察并记录发光二极管亮、暗情况与 CP 端手动脉冲个数的关系。

将输出换至数码显示，观察计数器的输出。

实验中 A、B、C、D 可悬空；LD、 $CT_P$   $CT_T$  接高电平；CR 接数据开关；CO 接发光二极管。

#### 4. 分别连接 10 进制和 6 进制加法计数器

计数器输出连显示译码电路。

首先用手动的方法，向 CP 端送入计数脉冲，检查功能是否正确。

手动检查无误后，再用实验箱上的秒信号作为输入脉冲

#### 5. 分别连接 60 进制和 24 进制加法计数器

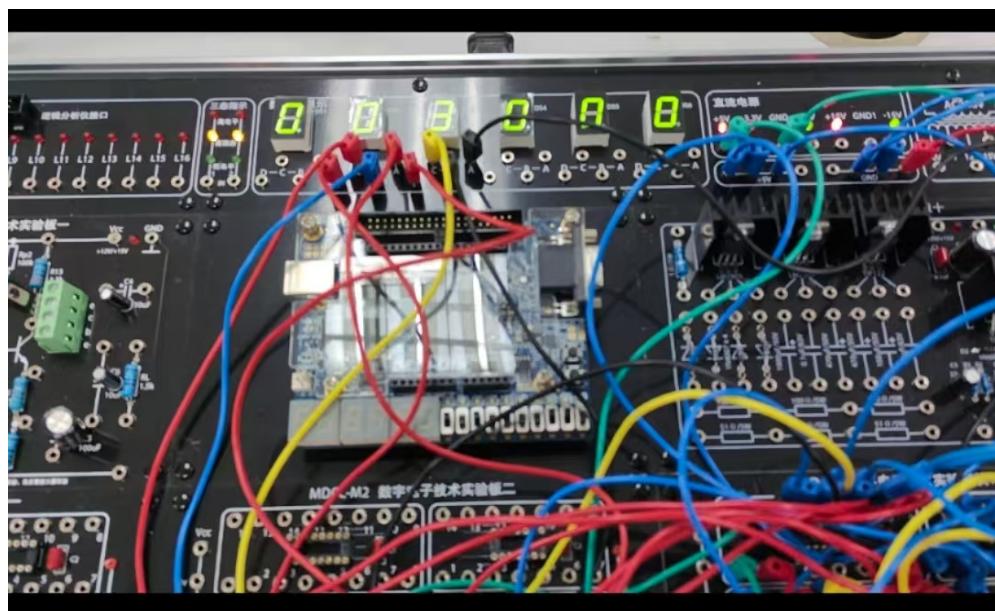

将十进制和六进制进行级联，然后再将十进制的输出和六进制的输出，分别与两个显示电路（D、C、B、A）连接、测试。完成能显示“分”或“时”的电路。

### 五、实验结果与分析

1. 测试阶段，译码管能正确显示二进制数字，结果如下：芯片与非门和计数功能均正常 2. 计数器都正确完成了

| 输入   | 显示 | 输入   | 显示 |

|------|----|------|----|

| 0000 | 0  | 1000 | 8  |

| 0001 | 1  | 1001 | 9  |

| 0010 | 2  | 1010 | 灭  |

| 0011 | 3  | 1011 | 灭  |

| 0100 | 4  | 1100 | 灭  |

| 0101 | 5  | 1101 | 灭  |

| 0110 | 6  | 1110 | 灭  |

| 0111 | 7  | 1111 | 灭  |

计数功能，交给老师验收。

## 六、心得与讨论

1. 通过本次实验，体会到数字逻辑电路的功能与特点，学习了用数字集成逻辑电路组装数字电路，并学习数字电路的调试方法。比如，在调试时，应分阶段连接调试，一步一步地进行。以本次实验为例，先连接好个位的十进制计数器，电路工作正确后，再接十位的六进制计数器。两者都正常后，再将 60 进制计数器连接起来。采用这种步步为营的接线和调试方法（称为自下而上），能较容易地发现问题并排除故障。

2. 老师还讲了许多 60 进制和 24 进制计数器可能会遇到的问题以及解决方法，如十位清零过快，需要加滤波电容来延时清零。

线

订

装